Commits on Source (12)

-

OBUZOR Grazia authored

-

OBUZOR Grazia authored

-

OBUZOR Grazia authored

-

OBUZOR Grazia authored

-

OBUZOR Grazia authored

-

Grazia OBUZOR authored

-

Grazia OBUZOR authored

Merge branch 'main' of https://gitlab-df.imt-atlantique.fr/tp-vhdl-mee/MEDCON/gr-vhdl-g24obuzo/tp-filtre-etudiant-g24obuzo

-

OBUZOR Grazia authored

-

OBUZOR Grazia authored

-

Grazia OBUZOR authored

-

Grazia OBUZOR authored

-

MENEGON XAVIER Joao Vitor authored

Showing

- docs/compte-rendu.md 9 additions, 5 deletionsdocs/compte-rendu.md

- docs/img/ControlUnitSequence.png 0 additions, 0 deletionsdocs/img/ControlUnitSequence.png

- docs/img/FSM.drawio.png 0 additions, 0 deletionsdocs/img/FSM.drawio.png

- docs/img/OperativeUnitSequence.png 0 additions, 0 deletionsdocs/img/OperativeUnitSequence.png

- docs/img/controlUnitTest1.png 0 additions, 0 deletionsdocs/img/controlUnitTest1.png

- docs/img/controlUnitTest2.png 0 additions, 0 deletionsdocs/img/controlUnitTest2.png

- src/hdl/controlUnit.vhd 37 additions, 13 deletionssrc/hdl/controlUnit.vhd

- src/hdl/operativeUnit.vhd 45 additions, 18 deletionssrc/hdl/operativeUnit.vhd

- vivado.jou 53 additions, 0 deletionsvivado.jou

- vivado.log 362 additions, 0 deletionsvivado.log

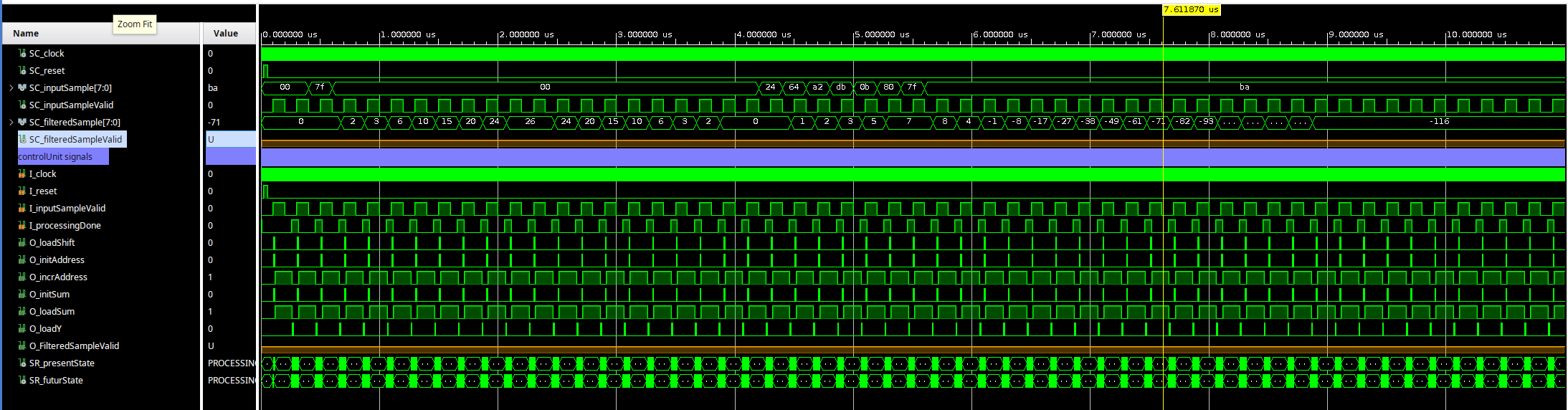

docs/img/ControlUnitSequence.png

0 → 100644

60.6 KiB

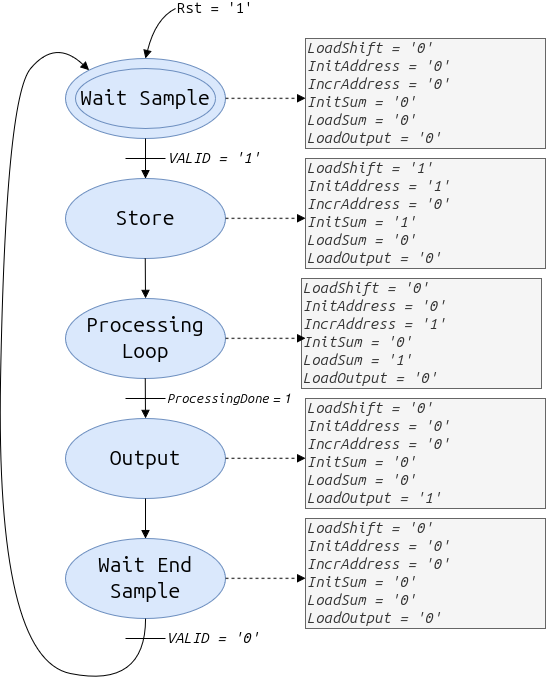

docs/img/FSM.drawio.png

0 → 100644

131 KiB

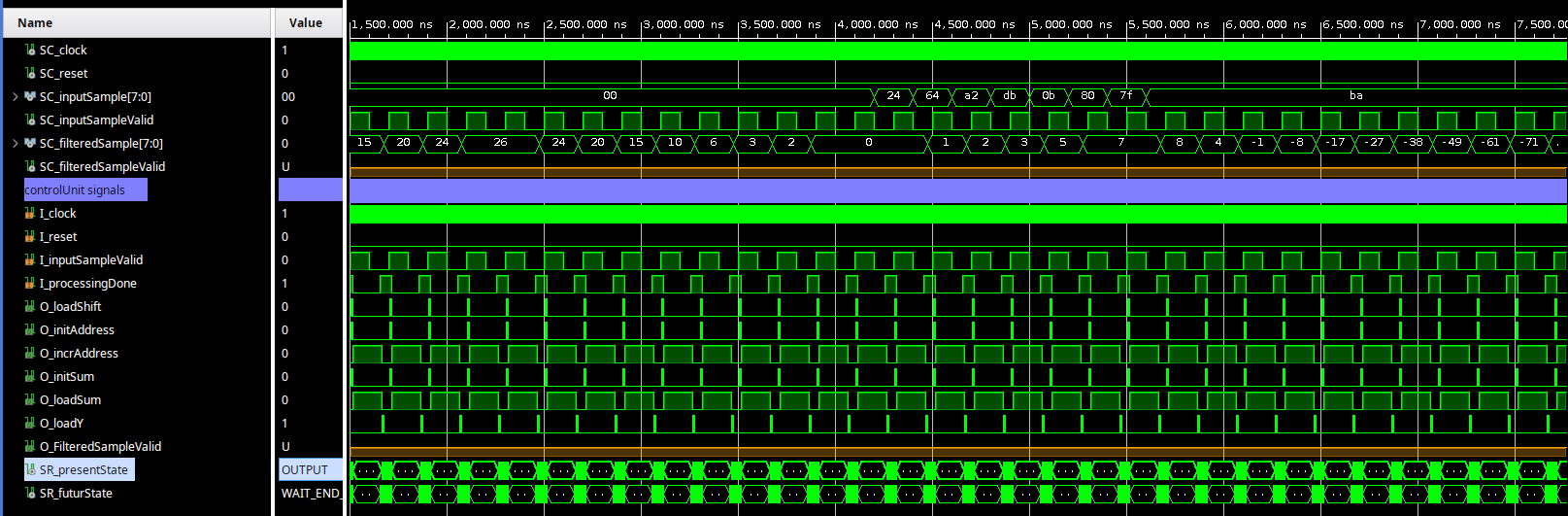

docs/img/OperativeUnitSequence.png

0 → 100644

54.2 KiB

docs/img/controlUnitTest1.png

0 → 100644

55.9 KiB

docs/img/controlUnitTest2.png

0 → 100644

57.9 KiB

vivado.jou

0 → 100644

vivado.log

0 → 100644

This diff is collapsed.