-

- Downloads

Session 1 : Rapport à modifier

Showing

- docs/compte-rendu.md 19 additions, 9 deletionsdocs/compte-rendu.md

- docs/image-1.png 0 additions, 0 deletionsdocs/image-1.png

- docs/image-12-1.png 0 additions, 0 deletionsdocs/image-12-1.png

- docs/image-12-2.png 0 additions, 0 deletionsdocs/image-12-2.png

- docs/image-12.png 0 additions, 0 deletionsdocs/image-12.png

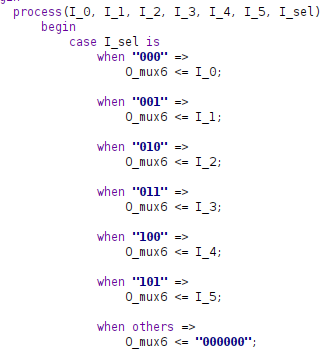

docs/image-1.png

0 → 100644

20.1 KiB

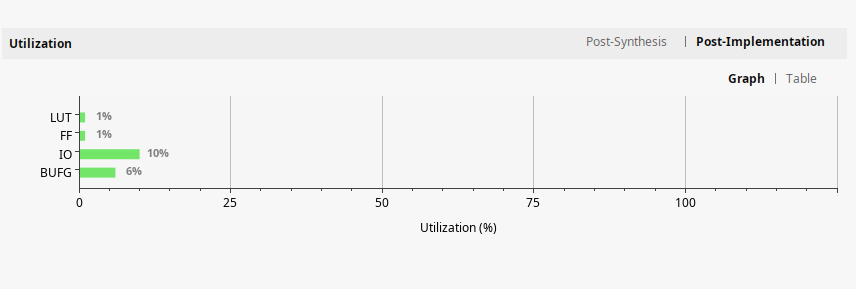

docs/image-12-1.png

0 → 100644

13.2 KiB

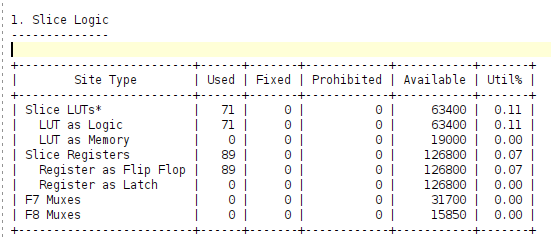

docs/image-12-2.png

0 → 100644

21.4 KiB

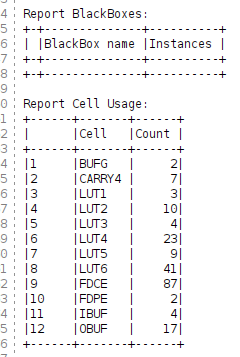

docs/image-12.png

0 → 100644

16.6 KiB