-

- Downloads

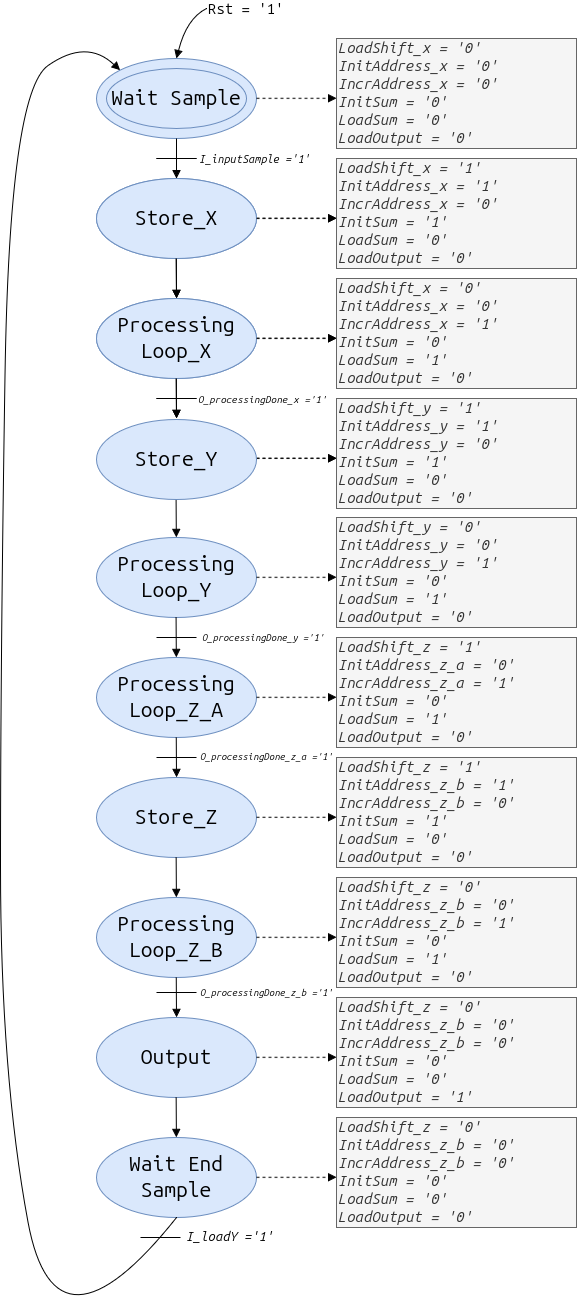

modification FSM finale + ajout du fichier vhdl

controlUnit.vhd

0 → 100644

docs/img/FSM_MEDCON.drawio

0 → 100644

This diff is collapsed.

docs/img/FSM_MEDCON.drawio.png

0 → 100644

264 KiB

264 KiB